2015/11/23

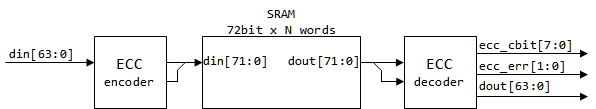

- 今回は実際にハミング符号のECC回路をRTLで書いてみました。例として、64bitのデータ幅を持つSRAMへの入出力データにECCを適用するケースを扱います。下記が全体の図になります。

Figure 1. 全体図 - 64bitのデータに対する検査bitは、前回やったように8bitです。従って64bitのデータに対し、SRAMとしては72bit幅を用意しています。

- SRAMの前段に置かれているのが、ECC encoderです。64bitのデータから8bitの検査符号を生成します。SRAMの後段に置かれているのが、ECC decoderです。SRAM内に置かれたデータが何らかの要因で変わってしまった際、検査bitのデータを利用してエラー訂正を行います。

- 一部行数が長いため、今回のRTLソースについては、こちら「

ecc_064_2015_0160a.v:Verilog-HDL」「ecc_064_2015_0170a.v:Verilog-HDL」(2015/11/29追記:間違えていたため訂正しました)を参照下さい

ECC Encoder

-

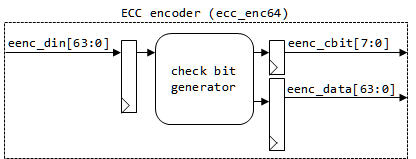

まずECC encoder(Module名:ecc_enc64)を見てみます。この回路は前回説明した検査bitを生成する回路で、作成した符号表に従って、ひたすら各データをExclusive ORします。

Figure 2. ECC encoder - 特にレジスタはいらないのですが、64bitのデータをEORするということは、EORのセルだけでも5段必要になるため、SRAMのレイアウト位置が固定されたFPGA等では動作速度で問題が発生しやすくなります。そのため、ECC encoder Moduleの入口と出口にレジスタを置いています。

- 図中のcheck bit generatorは、RTL中にて「ecc_cbg64」というmodule名で記述しています。このmoduleはECC decoderでも利用します。

- あと図中では書いていませんが、SRAMに対してWrite側のクロックとRead側のクロックが異なることもあるので、リセットの同期化回路は、ECC encoderとECC decoderに独立で置いています。今回のRTLでは同期化部を平文のRTLで書いて(手抜きして)いますが、ASICの場合「指定セルを置いて下さい」と言われることもあるので、本当を言うと、ここは独立Moduleとし、そのModuleを書き換えるようにした方が楽です。

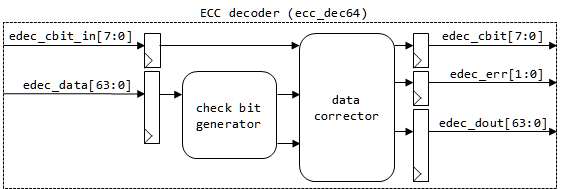

ECC Decoder

- SRAMの後段に置かれているのがECC Decoder(Module名:ecc_dec64)です。SRAMの出力データから再度検査bitを生成し、元々格納していた検査bitと値の比較をし、エラーがあれば訂正を行います。内部にレジスタが置かれている理由はECC encoderと同じ速度ケアです。

Figure 3. ECC decoder - ECC decoderの中に置かれているdata corrector(Module名:ecc_dc64)部で、データの訂正判定を行っています。data correctorのブロック図を示します。

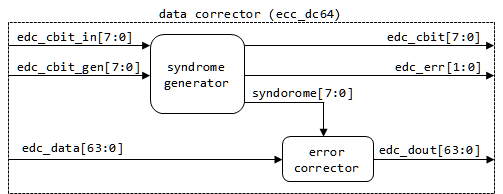

Figure 4. data corrector - syndrome generatorと書いてますが、要はSRAMからの出力データから生成した検査bitの値と、格納していた検査bitの値を比較し、不一致のbitに「1」が立つ、つまりExclusive ORしているだけです。syndorme[7:0]がその結果です。

-

syndrome[7:0]の値が指し示す状態を、edec_err[1:0]で出力しています。

(1) syndrome[7:0] が All-0 : 訂正無し → edc_err[1:0] = 2'b00;

(2) (1)ではなく、syndrome[7] が 0 : ダブルビットエラー → edc_err[1:0] = 2'b10;

(3) (1)(2)ではなく、syndrome[7:0]が検査bit表に無い値 : 想定外エラー → edc_err[1:0] = 2'b11;

(4) (1)(2)(3)に該当しない : シングルビットエラー → edc_err[1:0] = 2'b01;

- error correctorは、syndrome[7:0]の値から、64bitデータのエラー訂正を行います。syndrome[7:0]の値に従って検査符号表が指し示すデータbitを反転します。この論理は独立Module化せず、ecc_dec64内で直書きしています。

次は検証

- 今回時間都合で実装までしかできませんでした。全く検証していないので、今回のRTLではとんでもないチョンボをしているかもしれません。次回検証し、ミスがあればこちらにリンクしているRTLも修正したいと思います。

(2015/11/29追記:やはり間違えていたため訂正しました)。

2015/11/29 : RTL修正

Copyright(C) 2015 Altmo

本HPについて

本HPについて