2017/02/05

- True Dual Port SRAM(TDP SRAM)(*1)は、言うなればSingle Port SRAM(SP SRAM)としてのインタフェースを二組持ったSRAMと言えば良いでしょうか。ある程度データサイズが大きい場合、FPGA/ASICともにSRAMのマクロを使っても良いですが、小さい場合...例えば512bit未満等の場合は、マクロに置き換えずにFF(Flip-Flop)で記述したほうがパワー/面積とも抑えられることが多いです。

- このFFを使ってSRAM相当の機能を記述する場合ですが、SP SRAMの場合はSingle Clockなので、普通に書けば良いです。Dual Port SRAM(DP SRAM)の場合も、Single Clockは言うに及ばず、Write/Read Clockが別の場合も、FF側のクロックはWrite側を使用すれば良いため、これもそれ程は問題(*2)ないです。

- 問題はTDP SRAMです。Single Clockは他と同様に問題ありませんが、A/B port別Clockの場合は少し考える必要が出ます。port A側のクロックとport B側のクロック両方でWriteが発生するからです。しかもこれらのクロックは非同期想定となります。今回のレポートでは「Write Clockをどうするか」が話の中心になります。

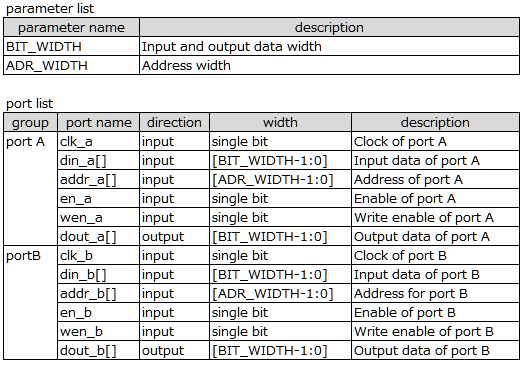

- 回路の話をする前に、ポート構成をクリアにしておきます。今回作成する非同期TDP SRAM FF版のパラメータとポートリストをTable 1 に示します。

表1.parameter and port list

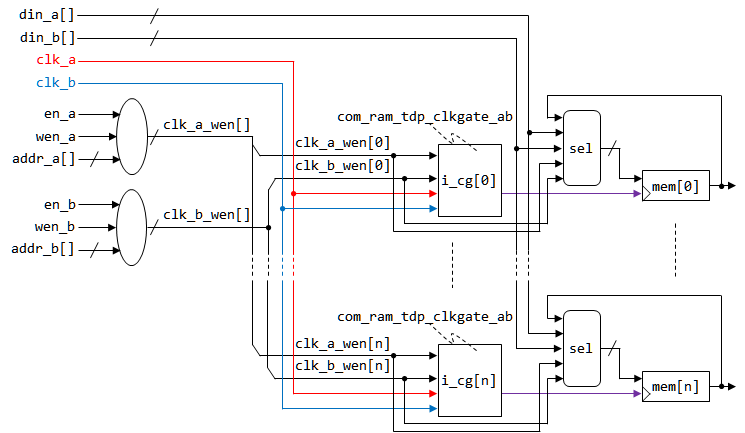

- 非同期TDP SRAM FF版のポイントは、A/B port Clock を Clock Gating回路を用いたセレクタを経由して、データ保持用に入れるという点です。とりあえず回路図を見て下さい。Figure 1 はWrite側論理を示しています。

Figure 1.非同期TDP SRAM FF版 Write側論理

Figure 1.非同期TDP SRAM FF版 Write側論理

-

Figure 1 の clk_a_wen[] 及び clk_b_wen[] に注目して下さい。これらの信号は、各アドレスに対してどのクロックからWriteが行われるかを示しています。これらの信号がクロックセレクタ i_cg[] に入り、mem[]レジスタへのクロックを制御しています。次はFigure 2にクロックセレクタの構造を示します。

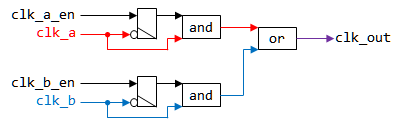

Figure 2.クロックセレクタ - 見ての通り、二つのクロックゲーティング回路出力をORしたものです。clk_a 及び clk_b それぞれについてはゲーティング回路でGlitchが出ないようにしていますが、clk_a/clk_bの同時enableについては全く対処されていません。つまりGlitchless Selectorではありません。

- ここをGlitchless Selectorにすると、クロックの切替にLatencyが発生します。言い換えると内部にPipelineを持たせる等でLatencyが許容できるならまた違った作り方も可能です。ですがTDP SRAMの場合同一アドレへの同時Write禁止は「お約束」なので、通常のSRAMと同じサイクルで操作できることを重視しました。禁止アクセスの検出はSimモデル側で対処する方針です。

-

RTL(RTL zip archive)は、非同期TDP SRAM FF版 である com_ram_tdp_async_reg.v と、そこから呼び出しているクロックセレクタの com_ram_tdp_clkgate_ab.v です。

- テストベンチ(test bench zip archive)は、テストベンチ(tb.v)と実行時のvcd(wave.vcd)が入っています。きれいにPASS/FAILを出すものではなく波形を見て動作確認するものです。手抜きですみません。

- 正直言ってなかなか無駄論理が付いています。なので使う機会は滅多に無いだろうなと思っています。実際合成した後にマルチクロックのSTAでどれほど文句を言われるか考えると気持ちがダウンします(^^;。あくまでお遊びということで...。

- SP/DP/TDP RAMについて詳しくは「Xilinxメモリリソースユーザーガイド」や「ALTERA Embedded Memory User Guide」を参照下さい。

- Read During Writeの動作も論理記述で補います。これはちょっと考えればわかるだろう話なので、いつか気が向いたら扱いたいと思います。

Copyright(C) 2017 Altmo

本HPについて

本HPについて