2017/10/22

- 低消費電力の設計を考えるとき、その方法の一つにクロック周波数の変更があります。例えば図1のようにPLLで速い周波数と遅い周波数を2本を出力し、それを状況によって切り替える等です。

図1: PLL出力クロックの切替 - ただし、クロックの切替は注意が必要です。例えば図2のようにクロック切替時にグリッチ(glitch)が乗ってしまった場合、それらのクロックを使用しているFFやメモリの値が壊れてしまうことがあるからです。

図2: クロックのグリッチによるFF値の破壊 - このグリッチを発生させないようにするには「クロックゲートを使って確実に止めてから切り替える」(*1)方法が基本となります。複数のクロックが関係するため、クロックゲートのEnable制御には非同期の要素が絡みます。今回、この点を考慮したクロックのMUXを作成してみました。

グリッチフリークロックMUX : IPat_GfClkMux

- 今回作成したグリッチフリークロックMUX IPat_GfClkMux(*2) のソースファイルは下記になります。

- IPat_GfClkMux_20171031A.zip (Clock gate low through latch を neg FFに変更)

IPat_GfClkMux_20171022A.zip

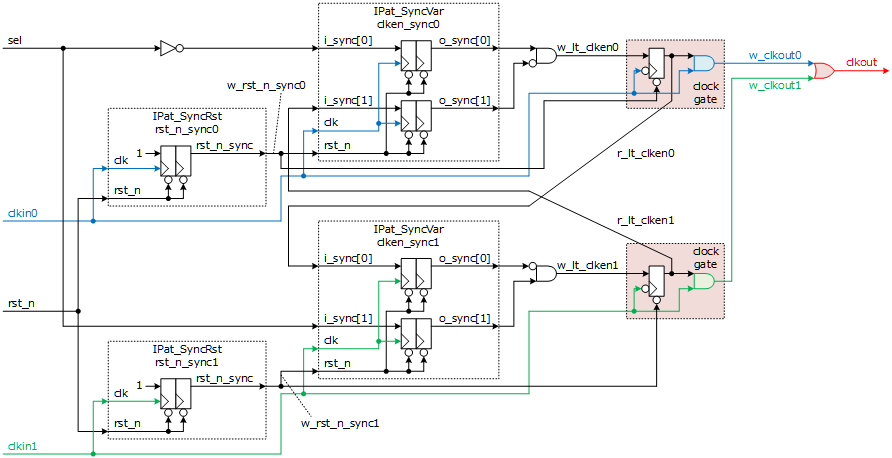

- 図3に作成した回路の構成を示します。左側がリセット同期化、中央がEnable同期化、右側がClock Gateになっています。

図3: IPat_GfClkMuxの構成(クリックで拡大します) - 表1にポートリストを示します。尚 IPat_GfClkMux にパラメータはありません。

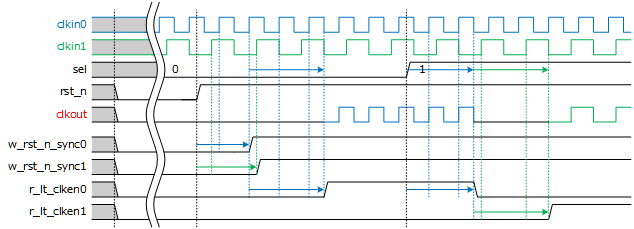

表1: IPat_GfClkMuxのポートリストPort name Direction Width Active Description clkin0 input 1 clock 入力クロック0 clkin1 input 1 clock 入力クロック1 sel input 1 select クロック選択(0:clkin0, 1:clkin1),非同期 rst_n input 1 0 非同期リセット clkout output 1 clock クロック出力 - 図4にタイミングチャートを示します。

図4: IPat_GfClkMuxのタイミングチャート

- リセットアサート(rst_n==0)中に、クロック入力安定化及びsel入力値確定を行って下さい。

- リセットデアサート後、内部で同期化を行った後、クロック出力が開始されます。

- sel信号を切り替えると、先に出力されていたクロックを停止してから切替が行われます。

注意点など

- 例として2入力clockの選択回路を作成していますが、結局のところ他のclockのenable状態を見て判定する論理を同期化してClock Gateに渡しているだけなので、同じ考え方で3入力だろうが4入力だろうが作成することができます。

- 今回作成した回路ではクロックパスに論理が入っているため、クロック解析が切れてしまうかもしれません。対策としてこのModuleの出力に、その製品で使用されるプロセスで提供される標準セルのPrimitiveバッファを置いて下さい。そのバッファの出力にタイミング制約としてクロック設定を行い、かつグルーピング指定による同期/非同期を設定して下さい。

- FPGAでは予めクロックツリーが実装されているので、合成可能な IPat_GfClkMux を使う前に、提供されているPrimitiveで機能が実現できないかを検討すべきと考えます。どちらかと言えば、このModuleはASICを意識しています。

- https://www.eetimes.com/document.asp?doc_id=1202359 を参照しています。

- 念のため書きますが、本Moduleを使用したことで得られる全ての結果についてAltmoは責任を負いません。

2017/10/31: Module修正

2018/09/01: リンク誤り修正(気付かなくてすみません...)

Copyright(C) 2017 Altmo

本HPについて

本HPについて