2022/02/26

- JTAG Boundary Scanとは、平たく言うと "ICのIOを制御する仕組み" のことです。この仕組はプリント基板の部品実装チェック等に利用されます。

- ICのIOは、そのICが持つ機能の一部であるため、IOを制御するためにICの機能を理解する必要があります。ですが部品実装者が全てのICの機能を理解して網羅的にIO制御を行うことは不可能(*1)です。

- しかしICの機能とは別に、IOを独立して制御する仕組みがあれば、ICの機能を理解しなくても部品間接続を確認することができます。更にその仕組が規格として統一されていれば、IC種別によらずIO制御が可能になります。

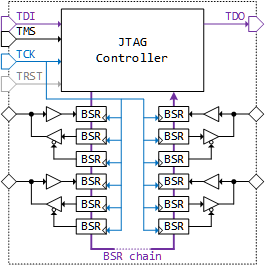

- その規格...IEEE 1149.1で規定されたIO制御のインターフェースがJTAG(Joint Test Action Group)です。このJTAGから内部のBSR(Boundary Scan Register)に値を設定することでIO制御を行います。

Figure 1: JTAG Boundary Scanの構成

JTAG Boundary Scanを利用した部品間接続テスト例

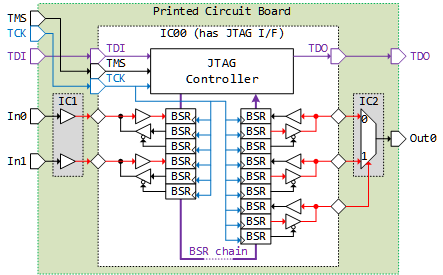

- 簡単な例を見てみましょう。仮にFigure 2のような、JTAG BSR I/Fを持ったICと組み合わせ論理の部品を持ったプリント基板があるとします。

Figure 2: プリント基板 - これらの部品が想定通りに接続されているかは、プリント基板自身のInput及び、JTAG BSRへ値を設定(Launch)した後、伝搬した論理値をBSRで捕捉(Capture)又はプリント基板のOutputを観測することで確認できます。

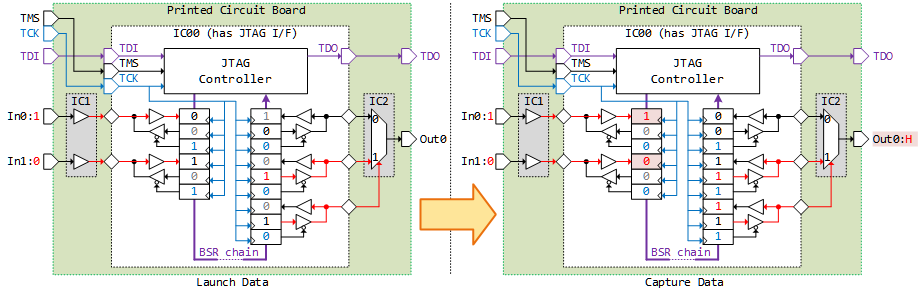

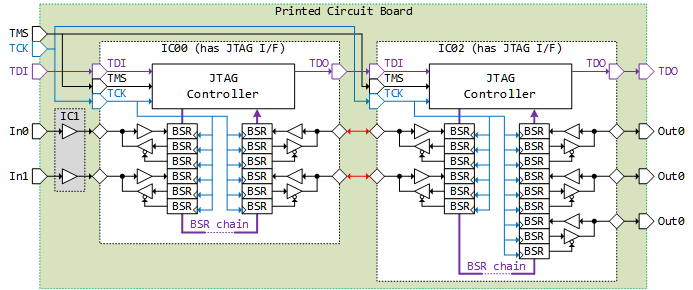

Figure 3: BSR Launch/Captureによる部品間接続の確認(クリックで拡大) - またプリント基板内に複数のJTAG I/Fを持つICがある場合、Figure 3のようにTDI/TDOポートをでデイジー接続することで、BSRを使ったIC間接続観測が可能になります。

Figure4 : JTAG BSRチェーンのデイジー接続によるIC間接続テスト(クリックで拡大)

ほとんどのFPGA/ASICがJTAG BSRを持つ

- ここまでの話、"何となくわかるけど、そもそもICがJTAG BSRを持ってる前提だよね?" という疑問があるかもしれません。このJTAG BSRですが、メジャーなFPGAはJTAG BSRを持っています。Configuraiton目的でJTAG IFを持ち、ついでにBSRも利用(*2)できるようになっています。

- そしてASICの場合ですが、恐らくオプションとしてJTAG及びBSR実装の依頼が可能なはずです。予算が問題ならばJTAG ControllerとBSRをユーザ自身の設計に仕込んでしまえば良い(*3)です。

- 今回はJTAG Boundary Scanの概要を見てきました。次回はBSRの構造を扱いたいと思います。

- 多分システム設計者でも難しい。

- 特殊IO(LVDSやDDRに使用するSSTL等)はBSRが無いこともありますが、BSR時はMPIOに化けるケースもあるため、特に高速IFを持つFPGAではBSRの適用範囲をよく確認して下さい。

- その際BSRチェーンのリオーダリング及びロックアップラッチの挿入可と伝えると良いかもしれない。

2022/03/13: 図中Output Enableの極性変更(正→負)

Copyright(C) 2022 Altmo

本HPについて

本HPについて