2022/03/06

- 今回は値のLaunch/Capture対象となるBSR(Boundary Scan Register)の構造を扱います。

- BSRはIEEE 1149.1に規定されたものとして11種類(BC_0〜BC_10)あります。ですが特にFPGAを考慮した場合、回路構成の推察/理解が必要なのはBC_1, BC_2, BC_4の3種類で、他は後回し(*1)でOKです。

- これらのBSRセルが持つ機能については、SiliconTEST.jp様の記述を引用させていただきます。

- BC_1, BC_2

- 境界スキャンで用いられるスキャンレジスタであり,基本的で柔軟性が高い.入力セル,出力セル,コントロールセル,インターナル(内部観測)セル,および入出力ピン構成要素セルとして使用できる.

- 2個のフリップフロップ(キャプチャ(CAP)フリップフロップ,アップデート(UPD)フリップフロップ)および2個のマルチプレクサから構成される.

- 出力に接続されるマルチプレクサはMode信号で切り替えられる.このMode信号は,ノン・インベイシブ操作モード命令(BYPASS,IDCODE,PRELOAD,SAMPLE,USERCODE)に対してはセル入力の値を選択し,ピン・パーミッション操作モード命令(CLAMP,EXTEST,INTEST,RUNBIST)に対してはUPDフリップフロップの値を選択する.

- BC_2では、このセル自身のテストを実行するためには内部システム回路を経由必要がなく,BC_1に比べてこの点が改善されている.

- BC_4

- 境界スキャンで用いられるスキャンレジスタであり,入力信号がそのまま出力信号に接続される.このため回路遅延を生じないという利点がある.入力セル(クロックを除く)としては使用できない(*2).

- キャプチャ(CAP)フリップフロップおよび1個のマルチプレクサから構成される.アップデート(UPD)フリップフロップは実装されない.出力側のマルチプレクサも実装されず,セルへの入力がそのまま出力される.

- 出力に接続されるマルチプレクサがないので,命令に基づくMode信号も存在しない.

- 説明だけだと回路イメージを作りにくいですね。この回路イメージですが、Intel(Altera)のデバイス・ハンドブックに記述されている説明図が参考になります。

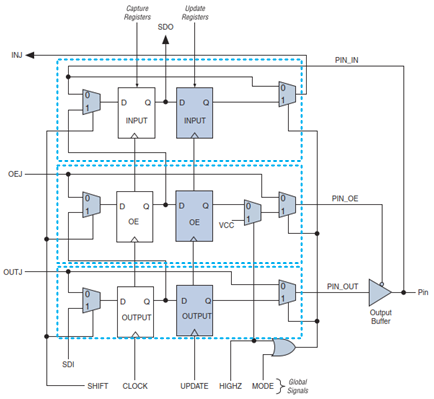

Figure 1: Cyclone V デバイスの IEEE Std. 1149.1 BST 回路付きのユーザー I/O BSC - Figure 1の水色枠内がBSRセルに相当します。1本の双方向IOピンを制御するのに3個のBSRセルを使っています。

- Intel(Altera)では、FPGAの通常IOにBC_1を使用しているとBSDLファイル(*3)に記述されているため、上記の水色枠部がBC_1の回路構造であると言えます。

- Update RegisterのクロックがUPDATEという制御信号名であることがちょっとあれです。一方Capture RegisterのクロックはCLOCKという名前もあれです。ShiftとCaptureの両方で動くので名前付けに迷ってCLOCKとしたように見えます。ですが、これはあくまで機能図なので実装は少し違うかもしれません。

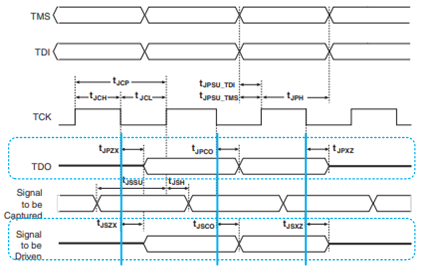

- そしてタイミング波形を注意して見ると、このUPDATEはTCKの立ち下がり(neg)エッジで動いている(*4)ようです。

Figure 2: IEEE Std. 1149.1 タイミング波形

BC_1, BC_2, BC_4の回路検討

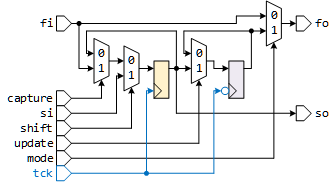

- ここまで集めた情報から、BC_1, BC_2, BC_4の具体的な回路を検討します。方針として、クロックにはなるべく論理を入れたくないのでtckを使用。shift/capture/updateについてはFFの入力論理信号とします(*5)。まずはBC_1です。

Figure 3: BC_1セル回路図 信号名 機能

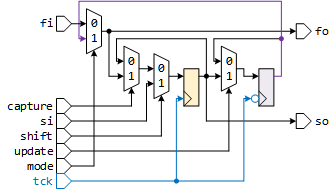

tck クロック fi ユーザー論理/システム論理入力 fo ユーザー論理/システム論理出力 si BSRチェーンシフト入力 so BSRチェーンシフト出力 shift BSRチェーンシフト制御(1=enable, 0=disable) capture Capture制御(1=enable, 0=disable) update Update制御(1=enable, 0=disable) mode fo出力選択(1=Update Register, 0=fi) - 次はBC_2セルです。Update Registerの値をCapture Registerで観測できるようにmodeセレクタの位置が変わっています。信号名はBC_1と同じです。

Figure 4: BC_2セル回路図 信号名 機能

tck クロック fi ユーザー論理/システム論理入力 fo ユーザー論理/システム論理出力 si BSRチェーンシフト入力 so BSRチェーンシフト出力 shift BSRチェーンシフト制御(1=enable, 0=disable) capture Capture制御(1=enable, 0=disable) update Update制御(1=enable, 0=disable) mode fo出力選択(1=Update Register, 0=fi) - 最後はBC_4セルです。BC_4はシステム論理への出力を持たないので、実質NCピン/未使用ピンに割り当てて使用します。

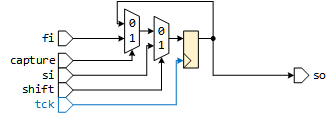

Figure 5: BC_4セル回路図 信号名 機能

tck クロック fi ユーザー論理/システム論理入力 si BSRチェーンシフト入力 so BSRチェーンシフト出力 shift BSRチェーンシフト制御(1=enable, 0=disable) capture Capture制御(1=enable, 0=disable) - さて、ここで示した回路はあくまで機能を実現するための実装例です。例えばEnable付きFFを使用すればセレクタの入り方は異なります。Update側にNeg-FFを使っていますが、Pos-FF+ロックアップラッチでも同じになります。

- shiftやcapture等のBSR制御はJTAGコントローラから行われます。つまりJTAGコントローラに設定されたインストラクションとステータスによってBSR制御信号の値は決まります。そこで次回はJTAGコントローラの構成を見たいと思います。

Copyright(C) 2022 Altmo

本HPについて

本HPについて