2022/03/12

- 今回はJTAG入出力とBSR制御を行うJTAGコントローラを扱います。まずはIC外部からアクセスする信号ですが、下記5信号が定められており、これらをまとめてTAP(Test Access Port)と呼びます。

Table 1: TAP(Test Access Port)

信号名 in/out 説明 TCK input クロック TMS input モードセレクト信号 TDI input シリアルデータ入力 TDO output シリアルデータ出力 TRST input コントローラリセット(オプション) - TCKはクロックです。Boundary Scanの場合、JTAGコントローラとBSRの両方でクロックとして利用されます。

- TMSはモードセレクト信号です。JTAGコントローラのステート制御を行います。

- TDIはシリアルデータ入力です。インストラクションやデータの入力に使用します。

- TDOはシリアルデータ出力です。TCK negエッジで出力されます。

- TRSTはJTAGコントローラのリセットですが、オプション扱いで実装のケースは稀です(*1)。

JTAGコントローラのコア側ポート

- 次はJTAGコントローラに存在するIC内部(コア)側のポート信号ですが、制御対象のBSRが持つポート依存(*2)です。前回のレポートでBSRの回路を検討しましたが、そこで列挙した信号がコントローラのコア側ポート構成を決めます。

Table 2: JTAGコントローラのコア側ポート例(実装依存)

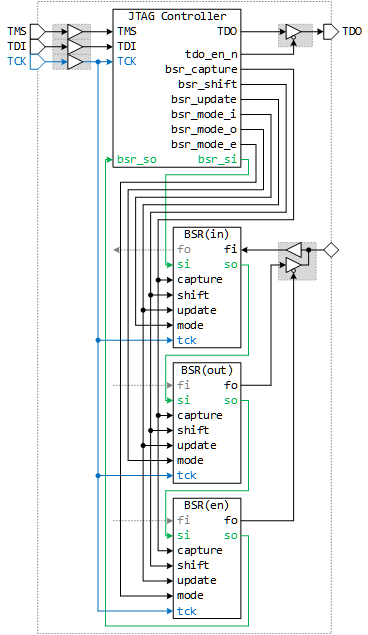

信号名 in/out 接続先 説明 tdo_en_n output TDO IOマクロのoutput enable TDOデータ出力/Hi-Zの切り替え制御 bsr_si output BSRチェーン最初のBSRのsi BSRチェーンへのデータ出力 bsr_so input BSRチェーン最後のBSRのso BSRチェーンからのデータ入力 bsr_capture output BSR capture BSRキャプチャ制御 bsr_shift output BSR shift BSRチェーンシフト制御 bsr_update output BSR update BSRアップデート制御 bsr_mode_i output IO入力側割当BSRのmode 入力 BSR mode制御 bsr_mode_o output IO出力側割当BSRのmode 出力 BSR mode制御 bsr_mode_e output IO出力Enable割当BSRのmode 出力Enable BSR mode制御 - これらの信号は、JTAGコントローラに設定されたインストラクション及び内部ステートによって適切に制御されます。Figure 1は1個の双方向IOを3個のBSRで制御する場合を例とした、JTAGコントローラとBSRの接続イメージです。

Figure 1: JTAGコントローラとBSRの接続例

JTAGコントローラのインスラクション

- JTAGコントローラに設定できるインストラクション(命令)は下記9種類が標準として定められています。これらのインストラクションの内BYPASS, EXTEST, SAMPLE/PRELOADは実装必須(Mandatory)です。またIDCODEはオプション(Optional)ですが、事実上必須として扱われます。

Table 3: JTAGコントローラのインストラクション命令 タイプ 説明 EXTEST Mandatory 基板上の部品間接続をテストするための命令です。 SAMPLE/PRELOAD Mandatory ICの現入力/出力値を取得(SAMPLE)した後、

BSRへ値をロード(PRELOAD)します。BYPASS Mandatory TDI/TDO間のシフトチェーンを1bitレジスタでバイパスします。 IDCODE Optional 部品識別の32bitレジスタ(DEVICE ID)をTDI/TDO間に接続します。

事実上Mandatoryです。HIGHZ Optional ICの出力ポートを全てオープン(ハイインピーダンス)にします。 CLAMP Optional ICの出力ポートにBSRで設定した値を適用します。

TDI/TDO間は1bitレジスタでバイパスされます。USERCODE Optional ユーザが設定できるレジスタ(USERCODE)をTDI/TDO間に接続します。

FPGA等ではConfiguration終了確認に利用できます。INTEST Optional BSRを経由してICの内部へ値を設定し、そのIC出力をBSRで取得します。 RUNBIST Optional IC内のBIST回路を実行し、その出力を取得します。 - 今回はJTAG Boundary Scanについてレポートしているため、USERCODE, INTEST, RUNBISTは扱いません。HIGHZとCLAMPは...まぁ...入れようと思います。HIGHZ命令を入れると、前回検討したBSRでHIGHZ制御の信号を持ったmoduleも必要ですね。これについては実装時に説明を追加します。

- 今回はここまでとして、次回はEXTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, HIGHZ, CLAMP命令について更に説明したいと思います。

2022/03/19: TDO output enable制御信号(tdo_en_n)追加

Copyright(C) 2022 Altmo

本HPについて

本HPについて