2022/03/20

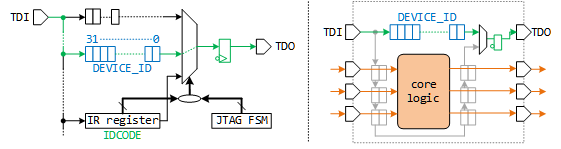

- 前回からの続きで、JTAGコントローラのインストラクション(命令)を説明します。最初はIDCODEです。

- IDCODEはIC毎に値が決められた32bitのレジスタ(DEVICE_ID)をJTAGコントローラのTDI/TDO間に接続する命令です。

- DEVICE_IDのシフト出力はLSB First([0]bitから)になります。

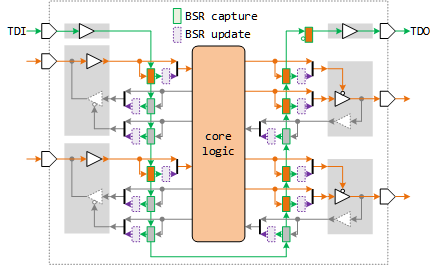

- ICのIOはCore Logicが制御し、BSRは関与しません。

Figure 1: IDCODE命令 - TDO手前にあるNegedge-FF(又はLow-Through-Latch)は、シフトチェーンにおけるロックアップラッチの役割を持ちます。IDCODE命令に限らず、TAP TDOポートの出力はTCK Negedgeで動きます。

- IDCODEはOptional命令ですが、メジャーFPGAでは「ほぼ実装」されており、JTAGコントローラに設定される命令初期値もIDCODEです(*1)。

- IDCODE命令で接続する32bitの値(DEVICE_ID)は下記のように割り当てられています。

[31:28] [27:12] [11:1] [0] Version

4bit部品番号(Part Number)

16bitメーカーID(Manufacturer ID)

11bit規定で'1'

1bit - DEVICE_ID(IDCODE_REGISTER)はBSDLファイルに記述されています。

Intel/Alteraの記述例 attribute IDCODE_REGISTER of MAX_10_10M08SAE144 : entity is

"0000"& --4-bit Version

"0011000110000010"& --16-bit Part Number

"00001101110"& --11-bit Manufacturer's Identity

"1"; --Mandatory LSB

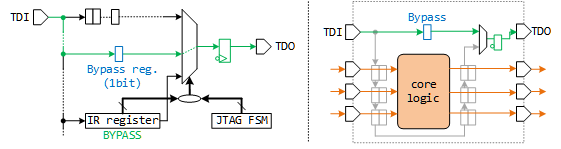

BYPASS

- BYPASSは1bitのFF(Bypass Register)をTDI/TDO間に接続する命令です。

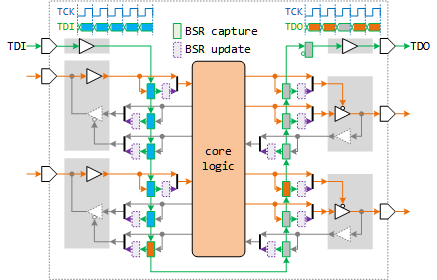

- ICのIOはCore Logicが制御し、BSRは関与しません。

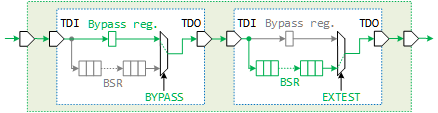

Figure 2: BYPASS命令 - 例えば下記のように、デイジー接続されたJTAG BSRを持つICが複数ある場合、文字通りBSRチェーン設定をバイパスするために使用します(TDO前のNeg-FFは省略)。

Figure 3: BYPASS命令使用例

SAMPLE/PRELOAD

- SAMPLE/PRELOADはTDI/TDO間にBSRチェーンを接続します。

- ICのIOはCore Logicが制御し、BSRは関与しません。

- BSRチェーンShift開始前に、ICへの入力及びCore Logicの出力をCapture-FFでCaptureします。

- BSRチェーンShift動作を行い、Captureした値をTDOから観測すると同時に、Capture-FFに値をロードします。

- BSRチェーンShift動作終了後、Update-FFにCapture-FFの値を入れます。

- Update-FFの値はCore Logicに影響せず、IOはCore Logicが制御し続けます。

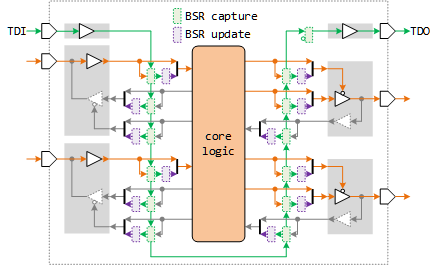

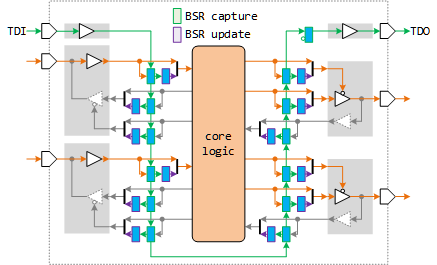

- 上記説明を図示してみます。Figure 4はBSR内のCapture-FFとUpdate-FFを明示化したIO/BSR/Core Logicの接続図です。Capture/Shift/Updateの論理は細かすぎるので省略しています。

Figure 4: BSR内Capture-FFとUpdate-FFの明示化 - SAMPLE/PRELOAD命令設定時、BSRはIOの制御に関わらず、Core LogicがIO制御を行っています(*2)。BSRチェーンのShiftを開始する前に、BSRのCapture-FFがICへの入力及びCore Logicの出力をCaptureします。SAMPLE/PRELOAD命令のSAMPLEに相当する動作です。

Figure 5: IC入力及びCore Logic出力をBSR Capture-FFがCapture - 次にBSRチェーンのShiftを行います。先程Captureした値はTDOのシリアル出力として観測すると同時に、BSRへの設定値をTDIからシリアル入力します。

Figure 6: BSR設定値のShift入力とCapture値観測 - Shift終了後、Capture-FFの値をUpdate-FFに入れます。BSRに任意の値を設定しましたが、IOの制御はCore Logicが行っています。Shiftと合わせて、ここまでがPRELOADに相当する動作です。

Figure 7: BSR Update-FFへの値設定

EXTEST

- EXTESTもTDI/TDO間にBSRチェーンを接続します。

- ICのIOはBSRが制御します。この点以外、SAMPLE/PRELOADと同じです。

- BSRチェーンShift開始前に、ICへの入力及びCore Logicの出力をCapture-FFでCaptureします。

- BSRチェーンShift動作を行い、Captureした値をTDOから観測すると同時に、Capture-FFに値をロードします。

- BSRチェーンShift動作終了後、Update-FFにCapture-FFの値を入れます。

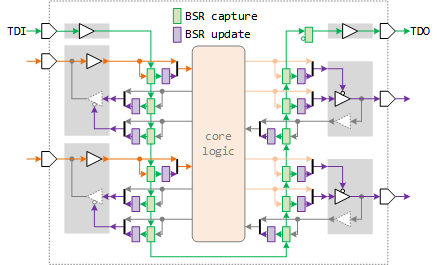

- Update-FFの値でBSRによるIOの制御が変化します。

Figure 8: EXTEST時のBSRによるIO制御 - もう少し簡単に説明すると、ICへの入力はBSRでCaptureし、ICからの出力はBSRでDriveするのがEXTESTです。BSRだけを使用してICの入力観測と出力制御を行います。

- 特にFPGAの場合、Configuration前のIO制御は全てHi-Z(Output Disable)になっているので、実装基板で要求されるIOの方向(Input/Output)をSAMPLE/PRELOAD命令で設定後、EXTEST命令で反映させます。以後はEXTESTのままCapture及びLoadしながらIC間接続テストを行います。

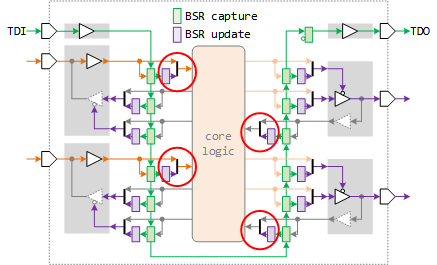

- 尚、EXTEST時もCore Logicに値を入力するBSRは入力値をそのまま伝搬(赤丸部)させます。このCore Logicに値を入力するBSRのUpdate-FFが使用されるのはINTEST/RUNBIST命令のときだけです。Boundary ScanによるIC間接続テストに関係するJTAG命令では使用されません。

Figure 9: EXTEST時もCore Logic入力BSRは値をそのまま伝搬(赤丸部)

HIGHZ

- HIGHZは、ICのOutputを全てHi-Z(Output Disable)にします。制御にBSRを使用せずHIGHZ命令設定時にOutputを全てHi-Zにします。

- FPGAはConfigurationに使用する特別なIOとTAP以外、全てIOとして双方向のため、全通常IOがHi-Zになります。

- 前々回のレポートで検討したBSRセル、そして前回のレポートで検討したJTAGコントローラのポート構成では、HIGHZ制御に関して何も書いていません。今後のレポートで実装検討時に追加したいと思います。

CLAMP

- CLAMPはBYPASSと同様に1bitのFF(Bypass Register)をTDI/TDO間に接続する命令です。

- しかし、CLAMPではIOの制御をBSRが行います。EXTESTやSAMPLE/PRELOADで設定したBSR値によるIO制御を維持(Clamp)したまま、BSRチェーンをBypassするために使用します。

次回は

- ようやくBoundary Scanに関係するJTAGインストラクション(命令)の説明が終わりました。JTAGコントローラは、ここで説明したインストラクションの値と、ステートマシンの値によって制御を決めています。次回はJTAGコントローラのステートマシンと、インスラクション/ステート/各制御信号の関係を説明したいと思います。

- 上記説明が終われば、やっとBSR及びJTAGコントローラのRTL実装に入ります...。

Copyright(C) 2022 Altmo

本HPについて

本HPについて