2022/03/27

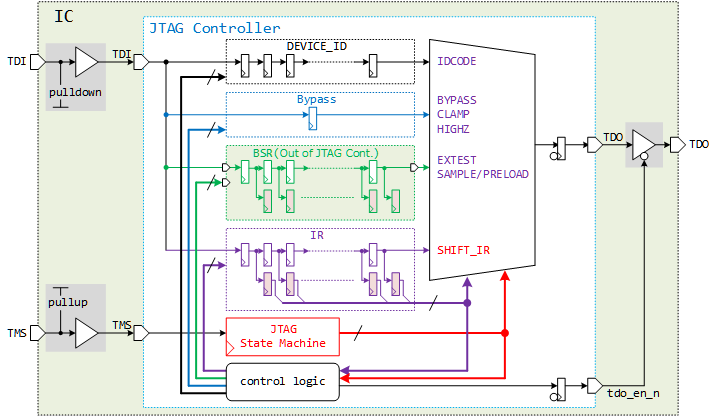

- 前回はJTAGコントローラのインストラクションを説明しました。そこで思い出して欲しいのが、その説明の中でよく出てきた言葉「〜は〜をTDI/TDO間に接続する」です。

- 接続する対象は、BYPASS/DEVICE_ID/BSR...何かしらのシフトチェーンです。そのシフトチェーンのレジスタが何かを制御する場合、シフト時も値を維持できるようにUpdate-FFを持っています。これはIOを制御するBSRがその例です。

- ならばJTAGの命令(Instruction)も同じ仕組みで設定できるようにしたらコントローラはシンプルになりますね。命令レジスタ(IR:Instruction Register)も、シフト中に値が動くと困るのでBSR同様Update-FFを持たせます。

- あとは命令に選択されるチェーンのCapture/Shift/Updateを制御するステートマシンを付ければ、JTAGコントローラの大まかな構造ができあがります。

Figure 1: JTAGコントローラの構造(クロックTCKは省略) - Figure 1でわかるように、IRに設定された命令によって、Capture/Shift/Updateの対象となるチェーンが決まります。このIRの値によって選択されるシフトチェーンをデータレジスタ(DR:Data Register)と呼びます。

Table 1: IRと選択されるDRの関係

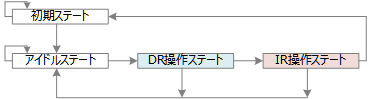

IR IDCODE BYPASS CLAMP HIGHZ EXTEST SAMPLE/PRELOAD DR DEVICE_ID Bypass Bypass Bypass BSR BSR - IRの値によって操作対象のDRを決めますが、IRの設定操作は別に必要です。よってJTAGコントローラのステートマシンは、大分類として下記状態を持つことになります。

Figure 2: JTAGステートマシン(大分類)・初期ステート

・アイドルステート

・DR操作ステート

・IR操作ステート

JTAGコントローラのステートマシン

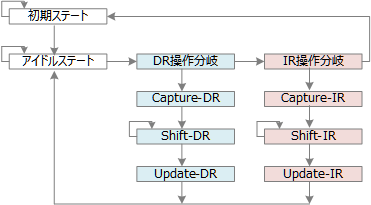

- では、DRもしくはIRといったレジスタの操作をもう少し細かく見てみましょう。とは言うものの、DR/IRは結局シフトチェーンなので操作は同じです。Capture/Shift/Updateのステートを明示化するだけです。

Figure 3: DR/IR操作のCapture/Shift/Updateステート明示化・Capture:

- Shift開始前に観測値Capture

・Shift:

- Capture値Shift出力

- 設定値Shift入力

・Update:

- Shift入力値をUpdate-FFに反映

- この段階で「どっかで見たことある図に似てきたな...」と感じている(*1)のではないでしょうか。このステートマシンはBoundary Scanを扱うステートを抜き出した結果になります。

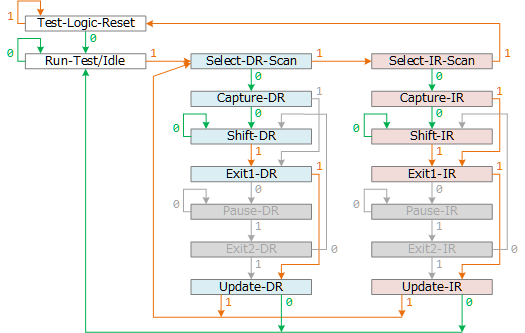

- ここでIEEE 1149.1に定められたJTAGのステートマシンをFigure 4に示しますが、Boundary Scanを使用した部品間接続テストで意識するステートはFigure 3に示された部分だけです。Shiftのスキップや中断制御がステートマシンに加わっていますが(えいやで言うと)使いません。尚、ステートの遷移はFigure 1でも示したようにTMSが制御します。

Figure 4: IEEE 1149.1に定められたJTAGステートマシン - Figure 4のJTAGステートマシンは16の状態を持っています。ステートを4bitのレジスタで保持した場合、何かでレジスタの値が不定でも必ずどこかのステートになるため「全く戻れない」という状況にはなりません。

- 最もTest-Logic-Resetから遠いCapture-DR/IRステートでも、TMS=1の状態でTCKが5クロック入ればTest-Logic-Resetに戻ります。FPGAやASICでTMSに割り当てる入力IOにPullupを付ける理由(*2)です。また、コントローラのリセット信号であるTRSTがオプション扱いになる理由でもあります。

後は制御信号の真理値表とタイミングチャート

- 今回はJTAGコントローラのブロック図とステートマシンを扱いました。

- あとはレジスタ名と制御信号名を決めて、レジスタ初期値とIR/ステートマシンの値に対する制御信号の真理値表を作れば、コントローラの仕様作成が完了します。

- 更にシミュレータ/オシロ観測によるデバッグに備えてタイミングチャートも作ります。これらは次回レポートにて。

2022/04/01: Figure 1 信号名修正 (誤)bsr_en_n→(正)tdo_en_n

2022/04/03: Figure 1 tdo_en_n Neg-FF出力追加

Copyright(C) 2022 Altmo

本HPについて

本HPについて