2022/05/21

- 前回のレポートではJTAGコントローラの仕様を検討/確認しましたが、実際にJTAGコントローラのRTLを書いてみました。

- JTAG Controller: IPat_JtagCont.v

※ステートマシンのバグを修正しました(2023/06/18)。

- JTAG Controller: IPat_JtagCont.v

- 設定値はパラメータとしているため、値の変更によってIC毎に異なるJTAG制御に対応します。設定変更を必要とするパラメータは前回レポートの"Table 4: JTAGコントローラのパラメータ(1)"を参照してください。

- 下記はJTAGコントローラのインスタンス記述例です。

IPat_JtagCont #( .P_WD_IR(6), .P_IR_IDCODE(6'b001001), .P_IR_SAMPLE(6'b000001), .P_IR_EXTEST(6'b001111), .P_IR_BYPASS(6'b111111), .P_EN_HIGHZ(1'b1), .P_IR_HIGHZ(6'b001010), .P_EN_CLAMP(1'b0), .P_DEVICE_ID(32'bxxxx_0100000_000000100_00001001001_1) //(注)Xを含む ) ins_IPat_JtagCont ( .TCK(w_jtag_tck), ...

作成したBSRモジュール

- JTAGコントローラと一緒にBSRモジュールも作成しています。仕様については以前のレポートを参照ください。尚モジュール名にHighZが付いたものは"highz"入力ポートを持ち、output enableを制御するBSRに適用します。

- BC_1: IPat_BsrBC_1.v

- BC_1: IPat_BsrBC_1_HighZ.v (with highz port)

- BC_2: IPat_BsrBC_2.v

- BC_2: IPat_BsrBC_2_HighZ.v (with highz port)

- BC_4: IPat_BsrBC_4.v

BSDLからBoundary Scan Simulationモデルを作成する

- JTAGコントローラとBSRモジュールがあれば、これらを組み合わせてBoundary Scan動作時のSimulationモデルを作成することができます(*1)。対象のICが持つポート名や、サポートするJTAGインストラクション、BSRの種類及び接続順は、BSDLファイルに記述されています。

- 下記はXilinx(AMD)とAltera(Intel)のFPGA BSDLサンプルです。

- XA6SLX25_CSG324.zip : Xilinx/AMD: Spartan6

- 10M08SAE144.zip : Altera/Intel: MAX10

- このBSDLを読んでFPGA/ICのSimulationモデルを作成しますが、とりあえず上記2つのBSDLを読むPerlモジュールを作りました。IPat_ReadBsdl.pm です。更に今回の確認用で汎用性を意識していません(*2)が、IPat_ReadBsdl.pm のオブジェクトを使ってSimulationモデルを作成するPerlモジュールも作成しました。IPat_GenBsrMod.pm です。

- 使用方法

- use lib './perl_module'; # モジュール置き場所指定

use IPat_ReadBsdl;

use IPat_GenBsrMod;

...

# ==== BSDLファイル読み込み(zipファイルは読めないので注意) ====

my $bsdl = IPat_ReadBsdl->new("BSDLファイル名");

# ==== BSDLオブジェクトRead ====

my $bsrmod = IPat_GenBsrMod->new($bsdl);

# ==== SimulationモデルWrite ====

# 引数はWriteファイル名(省略時は "entity名.v")

$bsrmod->writeBsrModel();

- use lib './perl_module'; # モジュール置き場所指定

- Simulationモデル作成例: XA6SLX25_CSG324.v

- 使用方法

- 上記Perlモジュールで作成したFPGAのBoundary Scan Simulationモデルは、先に説明したJTAGコントローラとBSRモジュール以外に、IO自身のモジュールも使用しています。これはSimulation用のBehaviorモデルです。

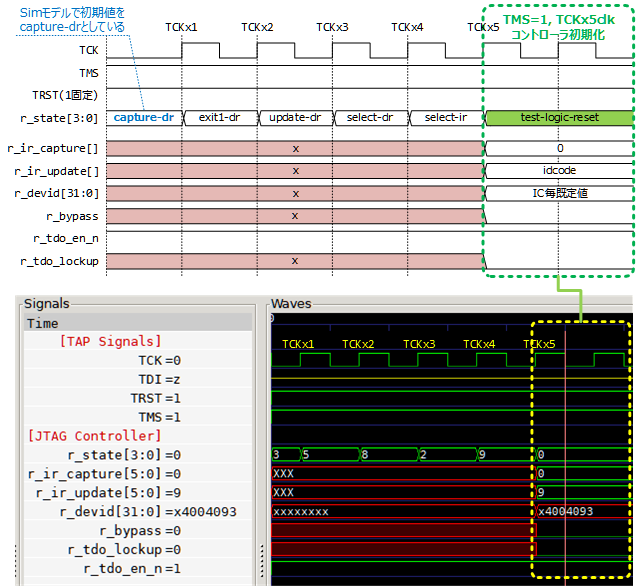

動作確認: JTAGコントローラ初期化

- サンプルとして作成した XA6SLX25_CSG324.v を使用して動作確認します。最初はJTAGコントローラ初期化です。

- サンプルはTRSTを持たないFPGAなので、JTAGコントローラのTRSTポートはモデル内で1固定です。初期化はTMS=1を維持してTCKを5cyc以上入力し、JTAGコントローラのステータスをTest-Logic-Resetに戻します。

Figure 1: JTAGコントローラ初期化(クリックで拡大。以後の図も同様です) - r_state[3:0]がJTAGコントローラのステートです。TCK 5cyc以降で0になっています。その際、他のレジスタも値が確定(初期化)されたことがわかります。

- r_tdo_en_nはJTAGステートのみで値が決まるため、Sim結果として確定出力になっています。

- r_devid[31:0]は初期化後もXを含みますが、これはBSDLに規定された値自身がXを含むためです。

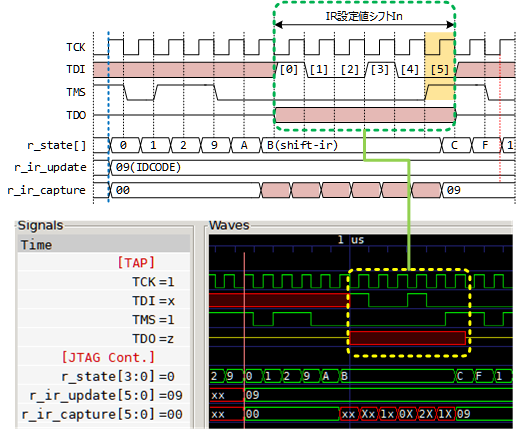

動作確認: IR設定とDEVICE_ID読み出し

- 次はインストラクション(IR)にIDCODEを設定して、DEVICE_IDを読み出しを行います。最初にインストラクションの設定です。初期化後IRがIDCODEのためr_ir_update[]に変化見えませんが、設定後もIDCODEが維持されます。

Figure 2: IR設定 - SHIFT-IR/DRステートにおけるシフトデータ入力の注意点ですが、最終bitの入力と同時にTMS=1とします。ここは直感的に理解しにくくミスしやすいところです(*3)。

- そして、全てのJTAGベクタで共通になりますが、TDI,TMS入力値はTCKの立ち下がり(Neg-edge)で変化させます。TDI,TMS,TCKは外部入力信号のため、TCK同期入力はできません。TCK Pos-edgeに対してSetup/Holdタイミングマージンを確保するため半サイクルずらしたNeg-edgeで値変化させます。

- JTAGは複数ICのTDO/TDIをデイジー接続することも可能ですが、TDOをNeg-edge出力とするのも同じ理由であり、ここからもTDI,TMSのNeg-edge入力はタイミング設定として必須になります。

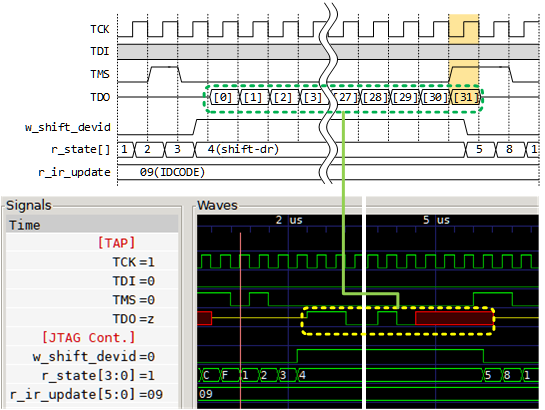

- 話を戻して、次はDEVICE_IDの読み出しです。すでにIRにはIDCODEが設定されているので、この状態でJTAGステートをSHIFT-DRにすれば、TDOからDEVICE_IDがシリアル出力されます。LSB-Firstです。

Figure 3: DEVICE_ID読み出し - DEVICE_IDのbit[0]は必ず1です。Figure 3のDEVICE_ID[28:31]が"X出力"なのは、XA6SLX25_CSG324.v の値としてBSDLに定義されているからです。

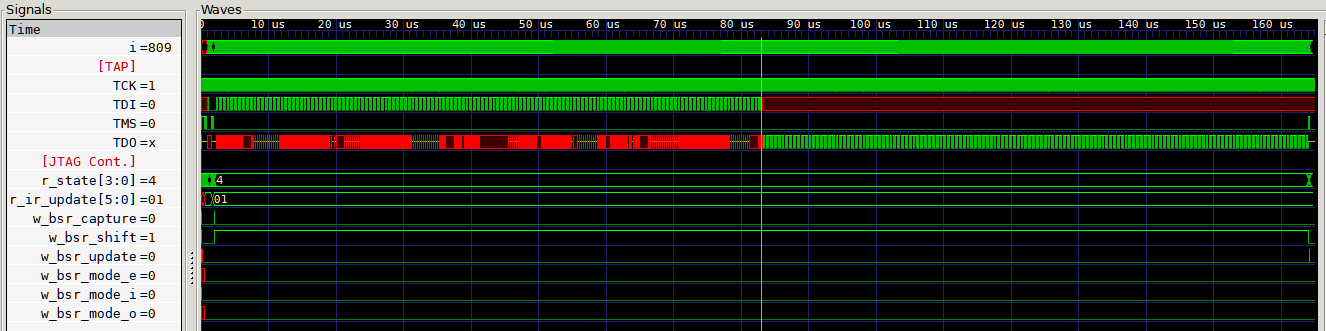

動作確認: BSR制御: SAMPLE/PRELOAD

- IR設定とシフト入出力をやってみて、そろそろJTAG制御に慣れたところでBSRの操作をしてみます。まずはSAMPLE/PRELOADです。

Figure 4: BSR SAMPLE/PRELOAD - TDIから値をシフトしてBSRチェーン長を超えたところでTDOに値が出てきます。本来SAMPLE/PRELOADは値の事前設定が目的なので出力するまでのシフトは必要ありませんが、IC/FPGAのBSRシフトが想定通り行われるかを外部信号で確認する場合、このようなSanityパターンが必要になります。

- IR設定がSAMPLE/PRELOADのとき、CAPTURE-DR/SHIFT-DR/UPDATE-DRを通してBSRのmode信号は0キープされています。BSRに値は設定されますが、IC内部及び外部への値は変化しません。

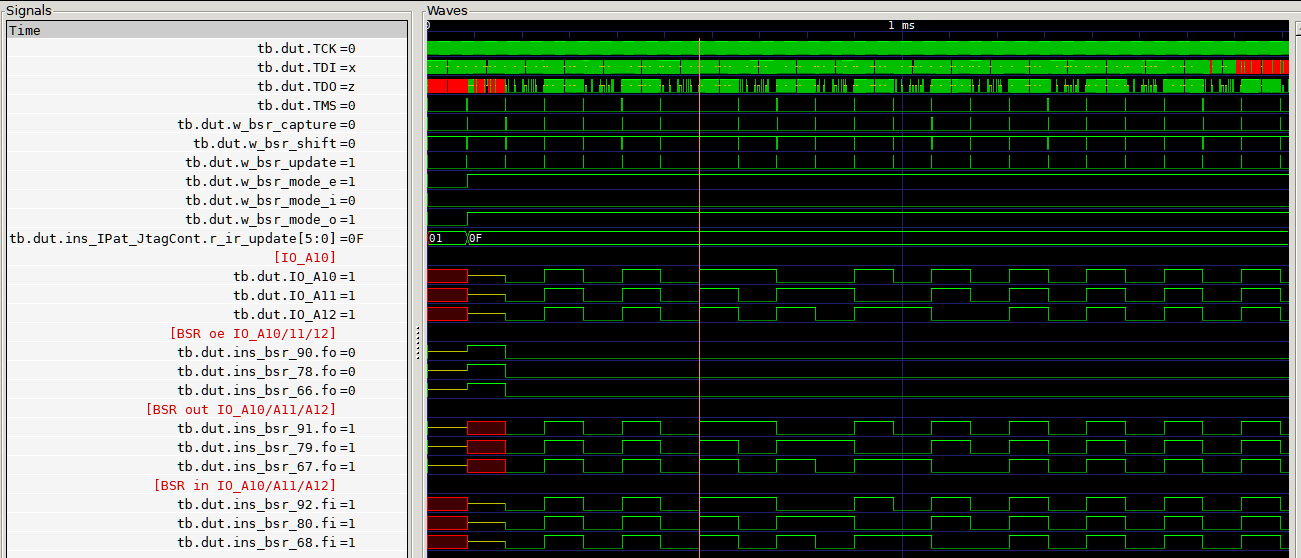

動作確認: BSR制御: EXTEST

- 次はEXTESTでIOを制御します。下記は全てのIOを出力にし、1本だけ他のIOと異なる出力(One-Hot又はOne-Cold)として、IOの接続をチェックするパターンです。モード信号bsr_mode_e/bsr_mode_oが1となり、UPDATE-DRでシフトしたBSR値が反映されます。

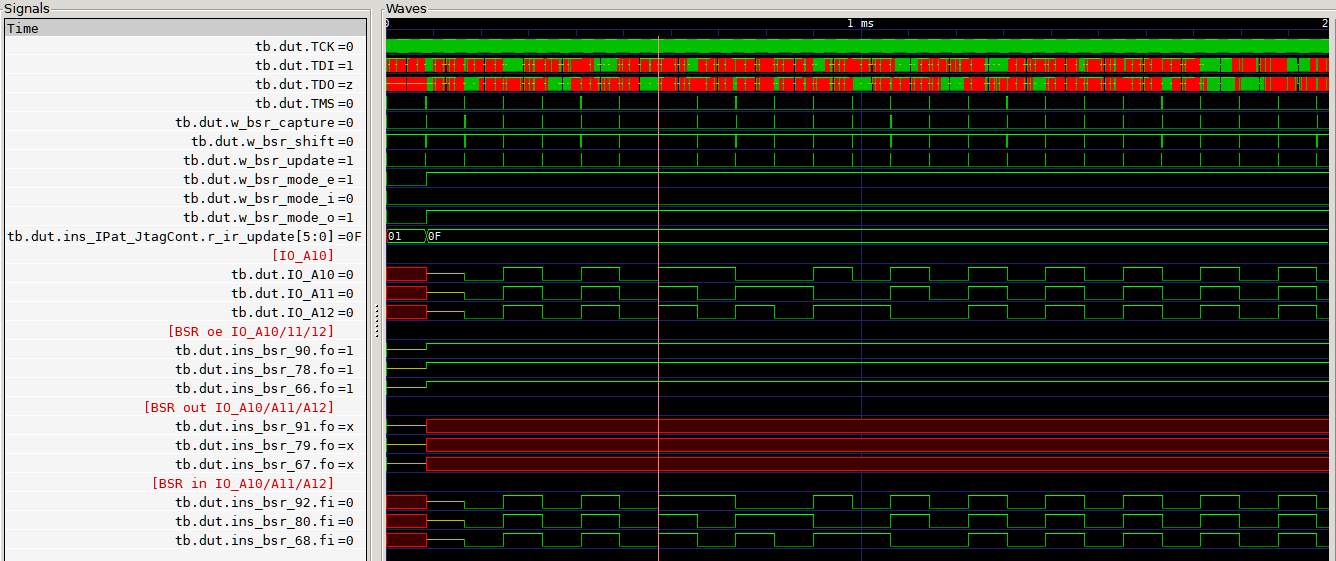

Figure 5: BSR EXTEST One-Hot/One-Cold Output - 次はIOからの入力(One-Hot又はOne-COld)をBSRでCaptureします。BSRのCapture結果はTDOシフト出力の結果が狙ったサイクル/bitに反映されたか見る(*4)必要があるので、波形だと確認しにくいですが、少なくともmode制御が正しいこと、BSRがinputになっていることは波形でも見えます。

Figure 6: BSR EXTEST One-Hot/One-Cold Input

次回はBSDLの説明

- 今回のモデルと波形を見て、JTAG Boundary Scanの動かし方は大体把握されたと思います。他の命令もIRをセットして、モード制御やTDI/TDOシフトの関係を確認すれば良いです。

- ようやく次回で最後...付録(Appendix)的な内容になりますが、BSDLの読み方とIPat_ReadBsdl.pmが持つデータ構造の関係を説明します。

2022-05-21: 初版

Copyright(C) 2022 Altmo

本HPについて

本HPについて