2024/02/04

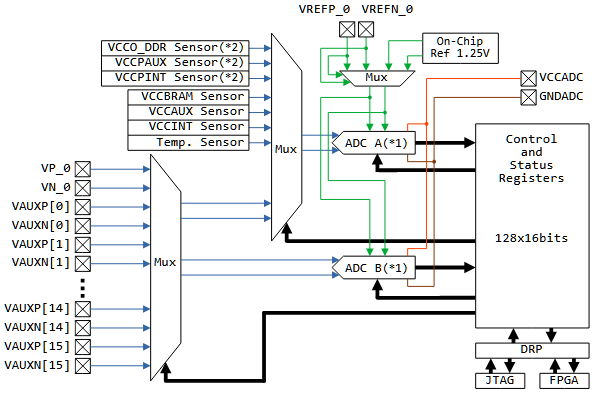

- 今回はXilinx 7 Series FPGAに搭載されたADコンバーターマクロであるXADCを扱います。XADCは17ペアチャンネルの外部アナログ入力、FPGA内部の電圧、内部温度センサ出力を取り込める多チャンネルADコンバーターです。Figure 1にXADCのブロック図(*1)を示します。

- AD変換対象

- 外部アナログポート(VP_0/VN_0, VAUXP/VAUXN[15:0])

- 全て差動入力です。17チャネル(差動ペア)あります。

- VP_0/VN_0はアナログ専用、VAUXP/VAUXN[15:0]は通常IO/アナログ兼用です。

- 入力電圧範囲 0〜1[V]、フルスケールは12bit(12'hFFF)です。

- 温度センサー

- チップ(ダイ)温度センサの値をAD変換します。

- 入力温度(ケルビン)範囲 0〜503.975[K]。フルスケールは12bit(12'hFFF)です。

- 電源電圧センサー

- VCCINT, VCCAUX, VCCBRAM の電源電圧をAD変換します。

- Zynq-7000 SoCでは VCCPINT, VCCPAUX, VCCO_DDR も加わります。

- 入力電圧範囲 0〜3[V]、フルスケールは12bit(12'hFFF)です。

- リファレンス電圧(1.25[V])

- 内部リファレンス利用/外部リファレンス入力を選ぶことができます。

- VREFP_0/VREFN_0ピンのを両方を0[V]とした場合、内部リファレンスを選択します。

- 制御方法

(*1)12-bit, 1MHz-Sampling (*2)Zynq-7000 SoCのみ搭載 |

ユニポーラ入力とバイポーラ入力

- XADCの外部アナログ差動入力信号は二種の入力モードを持ちます。

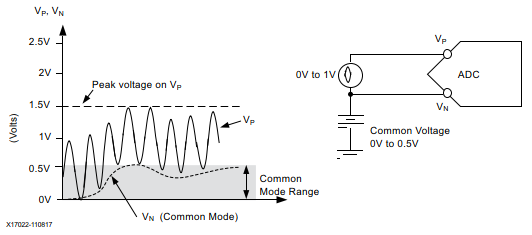

- ユニポーラ入力

- 0〜+1[V](正電圧のみ⇒ユニポーラ)が差動入力範囲。コモンの揺れ/オフセット含め最大入力値は1.5[V]。

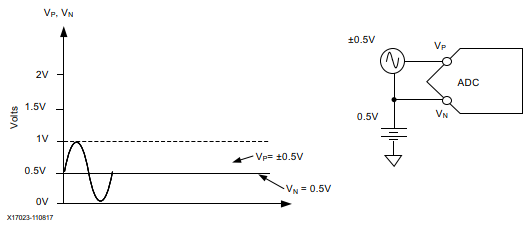

- バイポーラ入力

- ±0.5[V](正負電圧⇒バイポーラ)が差動入力範囲。

- 差動入力としての負電圧であり、差動P側入力絶対値は0〜1[V]。差動N側入力に0〜0.5[V]オフセット必要。

Figure 2: ユニポーラ入力(XADC資料より抜粋)

Figure 3: バイポーラ入力(XADC資料より抜粋)

XADCの動作モード(2024-02-18追記)

- XADCの動作モードには下記があります。動作の基本はシングルチャネルですが、XADCはチャネル数が多いため、その制御負荷を減らすシーケンサーを持ちます。初期状態はシーケンサー/デフォルトです。

- モード選択及び各モードの制御/設定レジスタをTable 2に示します。

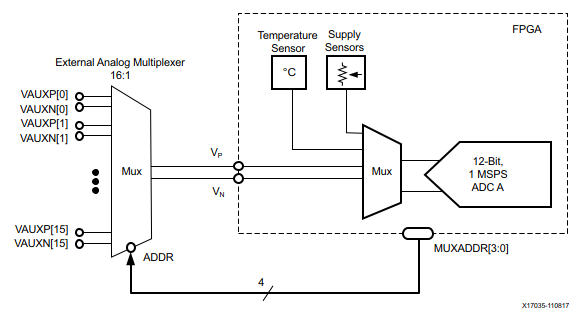

- 動作モードとしてあともう一つ、XADCは外部マルチプレクサモードを持ちます。FPGA外部のマルチプレクサを制御して、アナログ入力信号を選択します。

- 外部マルチプレクサモードは恐らくですが、基板アートワークの都合(*4)でFPGAへのアナログ信号入力を減らすためか、旧デザインからの継承目的と認識しています。

Table 1: XADCの動作モード

| 動作モード | 説明 | |

| シーケンサー | デフォルト | 電源電圧(VCC*)及び温度(Temp.)センサーの変換結果を自動格納する。 |

| シングルパス | 指定した複数指定チャネル変換一巡後、デフォルトに戻る。 | |

| 連続シーケンス | 指定した複数指定チャネル変換を繰り返す。デフォルトに戻らない。 | |

| 同時サンプリング | 16ペアチャネル外部入力(VAUXP/VAUXN[15:0])の内、2ペア([0,8]等)を同時変換。 | |

| 独立ADC | 変換対象はデフォルトと同じ。アラーム機能が追加される。 | |

| シングルチャネル | 変換対象チャネルを指定するモード。 | |

Table 2: モード選択及び各モードの制御/設定レジスタ

| 動作モード | モード選択値 CSR(41h[15:12]) |

動作設定CSRアドレス | |

| シーケンサー | デフォルト | 4'b0000 |

48h,49h: チャネル選択 4Ah,4Bh: 平均化 4Ch,4Dh: アナログ入力モード(ユニポーラ/バイポーラ) 4Eh,4Fh: セットリング時間 |

| シングルパス | 4'b0001 | ||

| 連続シーケンス | 4'b0010 | ||

| 同時サンプリング | 4'b01xx | ||

| 独立ADC | 4'b10xx | ||

| シングルチャネル | 4'b0011 | 40h: チャネル選択,平均化,アナログ入力モード,セットリング時間 | |

Figure 4: 外部マルチプレクサモード(XADC資料より抜粋)

次回は

- 説明のバランスを考えて、動作モードの説明を本レポート「XADCをJTAGで制御する(1)」に追記しました。次回はDRPインタフェースを経由したSimulationを扱います。

2024-02-04: 初版

Copyright(C) 2024 Altmo

本HPについて

本HPについて