2024/03/02

- 今回はDRPインタフェースを経由したXADCのSimulationを扱います(*1)。尚、Xilinx Vivadoはインストール済みと仮定します。そして今回のレポートではVerilog-HDLのモデルを扱います。

- 仮にVivadoがインストールされたフォルダを %Vivado_Path%、インストールVersionを %Ver% とすれば、下記のファイルをSimulationモデルとして使用します。自分のワークフォルダにコピーしてもOKです。

- %Vivado_Path%\%Ver%\data\verilog\src\unisims\XADC.v

- %Vivado_Path%\%Ver%\data\verilog\src\unisims\STARTUPE2.v

- %Vivado_Path%\%Ver%\data\verilog\src\glbl.v

- Simulatorも好きなものを使って下さい。Vivado付属のxvlog/xelab/xsimでも良いですし、iverilogでも良いです。

XADC.vのポート

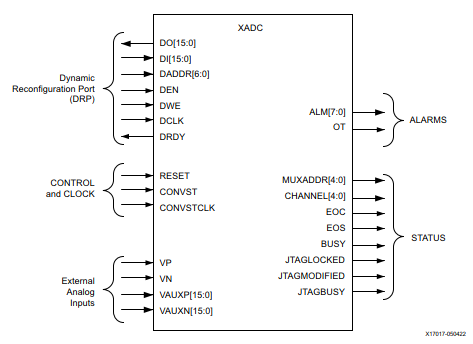

- XADC.vのポートをTable 1に示します。最初はデジタル入出力としてDRP系,RESET,CHANNEL,EOC,EOS,BUSYのみ使います。

Figure 1: XADC.vのポート(XADC資料より抜粋)

Table 1: XADC.vのポートリスト

| ポート | I/O | 説明 |

| DI[15:0] | input | DRP入力データバス |

| DO[15:0] | output | DRP出力データバス |

| DADDR[6:0] | input | DRPアドレスバス |

| DEN | input | DRPイネーブル[1:enable, 0:disable] |

| DWE | input | DRPライトイネーブル[1:enable, 0:disable] |

| DRDY | output | DRPデータレディ[1:active] |

| RESET | input | 制御ロジックリセット[1:assert(async), 0:de-assert(DCLK-sync)] |

| CHANNEL[4:0] | output | AD変換対象アナログチャンネル |

| EOC | output | AD変換終了[1:active] |

| EOS | output | AD変換シーケンス終了[1:active] |

| BUSY | output | AD変換実行中[1:active] |

| JTAGLOCKED | output | JTAGロック中[1:active] |

| Vp,Vn | input | アナログ専用入力ペア |

| VAUXP[15:0],VAUXN[15:0] | input | アナログ外部入力16ペア |

| CONVST | input | AD変換開始(*) |

| CONVSTCLK | input | AD変換開始クロック(*) |

| ALM[7:0] | output | 各種センサー(温度,VCCINT等)アラーム出力[1:active](*) |

| OT | output | 温度超過アラーム出力[1:active](*) |

| MUXADDR[4:0] | output | 外部マルチプレクサ制御(*) |

| JTAGMODIFIED | output | JTAGからDRPへ書き込み[1:active](*) |

| JTAGBUSY | output | JTAGからDRPアクセス中[1:active](*) |

DRPのタイミングチャート

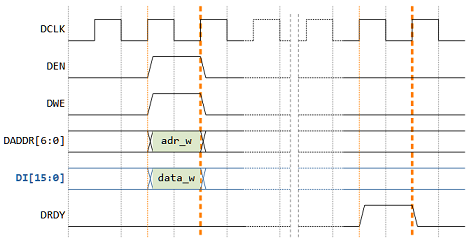

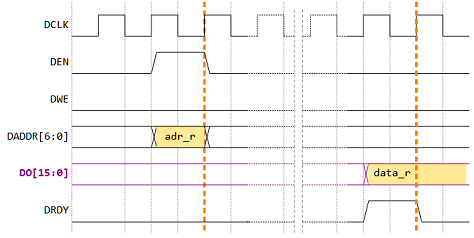

- DRPのタイミングチャートをFigure 2,3に示します(*2)。DRP系の信号は「DCLK同期」としています。

- DRP Writeでは、アドレス(DADDR[6:0])とデータ(DI[15:0])をセットしてから、CSRへ実際の書き込みが行われるとDRDY信号が1サイクルHigh出力になります。

- DRP Readでは、有効データが出力(DO[15:0])されると、DRDYが1サイクルHigh出力になります。

Figure 2: DRP Write タイミング

Figure 3: DRP Read タイミング

次回は

- DRP Simulationの続きとして、Analog入力設定と、CSR設定値を扱います。

Copyright(C) 2024 Altmo

本HPについて

本HPについて