2024/04/21

- デジタル回路の操作には当然ながらクロックが必要です。DRPのクロックはDCLKですが、これはどこから与えれば良いでしょうか。XADCはDCLKを外部から与えることもできますが、外部クロック停止時は自動で内部クロックに切り替わる仕掛け(*1)を持っています。

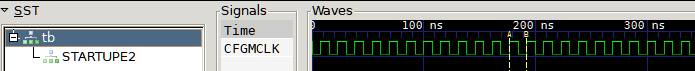

- この内部クロックはFPGA内のROSCから出力されています。FPGA Configurationに使用されるMCLKのことで、前回Simulationモデルの一つとしてSTARTUPE2.vを使用すると書いた理由になります。STARTUPE2.vの使い方は簡単です。インスタンスとして置くだけでクロックが出てきます。周期:15384[ps]、周波数:65[MHz]です(*2)。

- 本レポートシリーズでは、Configuration前のFPGAでJTAGを経由してAnalog入力を観測する予定なので、DRP経由のSimulationも内部ROSC(STARTUPE2)クロックを使用する方針とします。

List 1: テストベンチとiverilogによるSim実行

| テストベンチ | Simulation実行 | |

`timescale 1ps/1ps

module tb;

wire CFGMCLK;

STARTUPE2 STARTUPE2 (

.CFGMCLK(CFGMCLK)

);

initial begin

#(1000*1000*10) $finish;

end

initial begin

$dumpfile("wave.vcd");

$dumpvars(0, tb);

end

endmodule

|

>iverilog tb.v STARTUPE2.v glbl.v >vvp a.out >start gtkwave wave.vcd |

|

Figure 1: クロック出力波形

Analog入力の与え方

- 次は、外部アナログ入力信号や温度センサにどうやってアナログ値を与えるかですが...テストベンチでは外部アナログ入力信号もwireなのでぱっと思いつきませんね。

- この設定方法ですが、XADCではAnalog Stimulus Fileと呼ぶタブ/スペース区切りテキストファイルに各信号のアナログ値時間変化を書きます。ファイル名はXADCのパラメータSIM_MONITOR_FILEで定義され、デフォルトは"design.txt"です。

- List 2の例は10[us](=10000[ns])毎に、VAUXP/N[0] と VAUXP/N[1]の入力値が0.1[V]変化するという記述です。VAUXP/N[0]は初期値0.2[V]から0.1[V]ステップでUp、VAUXP/N[1]は初期値0.8[V]から0.1[V]ステップでDownします。

- Analog Stimulus Fileに記述できる項目名は下記が定義されています。項目の並び順に制約はありません。

List 2: Analog Stimulus File(design.txt)記述例

TIME VAUXP[0] VAUXN[0] VAUXP[1] VAUXN[1] 00000 0.2 0.0 0.8 0.0 10000 0.3 0.0 0.7 0.0 20000 0.4 0.0 0.6 0.0 30000 0.5 0.0 0.5 0.0 |

List 3: Analog Stimulus Fileに記述できる項目名

|

TEMP,

TIME,

VCCAUX,

VCCINT,

VCCBRAM,

VBRAM,

VCCPINT,

VCCPAUX,

VCCDDRO, VP, VN, VAUXP[0]〜[15], VAUXN[0]〜[15] |

CSRの設定

- ではDRP Simulationを行う際のCSR値を決めましょう。

- XADCは2種のサンプリングモードを持ちます。連続サンプリングとイベントドリブンサンプリングです。今回はCONVST信号を使用しない想定なので連続サンプリングモードを選択します。サンプリングモードの設定はCSR(40h[9])で行いますが、デフォルトが連続サンプリング(設定値0)になっているので、CSR設定はありません。

- 次は動作モードです。先のAnalog Stimulus File記述例に従って、VAUXP/N[0]とVAUXP/N[1]の2チャンネルを連続シーケンスで観測することにします。CSR(41h[15:12])に4'b0010を設定します。

- CSR(41h[15:0]) = 16'b0010_0000_0000_0000;

- 観測対象チャンネルはCSR(48h)又は(49h)で設定します。VAUXP/N[0]〜[15]はCSR(49h)です。bit番号がそのままVAUXP/N[*]のチャンネル番号に相当するので、チャンネル[0]と[1]を選ぶ場合は下記となります。

- CSR(49h[15:0]) = 16'b0000_0000_0000_0011;

- 最後は入力モード(ユニポーラ/バイポーラ)を設定します。デフォルトはユニポーラです。CSR(4ch)又は(4dh)でチャンネル毎に設定できますが、今回のAnalog Stimulus Fileはユニポーラ想定なので、CSR設定はありません。

次回は実際にSimulationを

- 今回でSimulationを実施するための情報整理が済みました。テストベンチとしてはリセット解除後に先のCSR設定を行い、後は変換フラグを見て、CSRからAD変換値をもらうことの繰り返しとなるでしょう。

- 次回はこのDRP Simulationのテストベンチ作成と実行結果波形を見ることにします。

Copyright(C) 2024 Altmo

本HPについて

本HPについて