2024/05/27

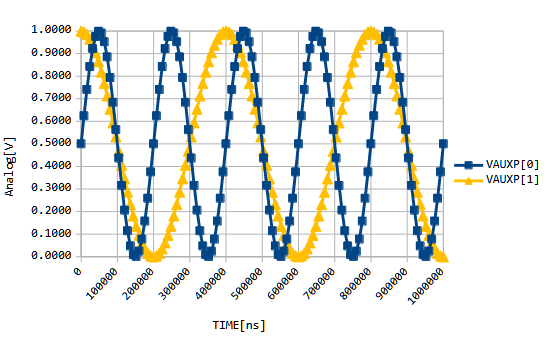

- 今回はDRPを経由したXADCのSimulationをやってみます。まずはAnalog入力の作成です。前回レポートで説明したように design.txt ファイル内にSim時間(ns単位)、アナログ入力の値(0.0〜1.0[V])を記述します。例として作成したのが、この design.txt(zip) です。最初の数行は下記のようになっています。

TIME VAUXP[0] VAUXN[0] VAUXP[1] VAUXN[1] 0 0.5000 0.0000 1.0000 0.0000 8000 0.6243 0.0000 0.9961 0.0000 16000 0.7409 0.0000 0.9843 0.0000 ...

|

テストベンチの作成と実行

- 次はテストベンチの作成です。ROSCとXADCのインスタンスを置いてXADCのDRPに入力するテストベンチです。今回例として作成したてテストベンチがこちらの tb.v です。

- テストベンチ内のDRPデータ入力部を抜き出しました。

initial begin

// 信号入力初期設定

#(0) tb_RESET=1'bx; tb_DEN =1'bx; tb_DWE=1'bx; cycles=1;

// RESET→DEN,DWE入力確定→RESET解除

#(CYC*1) cycles=cycles+1; tb_RESET=1'b1;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b0; tb_DWE=1'b0;

#(CYC*1) cycles=cycles+1; tb_RESET=1'b0;

// 観測対象チャンネル設定: VAUXP/N[1:0]

#(CYC*1) cycles=cycles+1; DADDR=7'h49; DI=16'b0000_0000_0000_0011;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b1; tb_DWE=1'b1;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b0; tb_DWE=1'b0;

// サンプリングモード設定:連続シーケンス:AD変換開始

#(CYC*1) cycles=cycles+1; DADDR=7'h41; DI=16'b0010_0000_0000_0000;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b1; tb_DWE=1'b1;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b0; tb_DWE=1'b0;

// 最初のAD変換が終わるまで待ち(デフォルトだと7〜8[us]程度)

for (i=0; i<8; i=i+1) begin

#(CYC*1) cycles=cycles+1;

end

// AD変換結果観測

$display("#TIME[ps]\t#DADDR[0]\t#DO[dec]");

for (i=0; i<100; i=i+1) begin

#(CYC*1) cycles=cycles+1; DADDR=7'h10; // VAUXP/N[0]

#(CYC*1) cycles=cycles+1; tb_DEN=1'b1;

#(CYC*1) cycles=cycles+1;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b0;

$display("%0t\t%b\t%d",$stime, DADDR[0], DO);

#(CYC*1) cycles=cycles+1; DADDR=7'h11; // VAUXP/N[1]

#(CYC*1) cycles=cycles+1; tb_DEN=1'b1;

#(CYC*1) cycles=cycles+1;

#(CYC*1) cycles=cycles+1; tb_DEN=1'b0;

$display("%0t\t%b\t%d",$stime, DADDR[0], DO);

end

// Simulation終了

#(CYC*1) cycles=cycles+1; $finish;

end

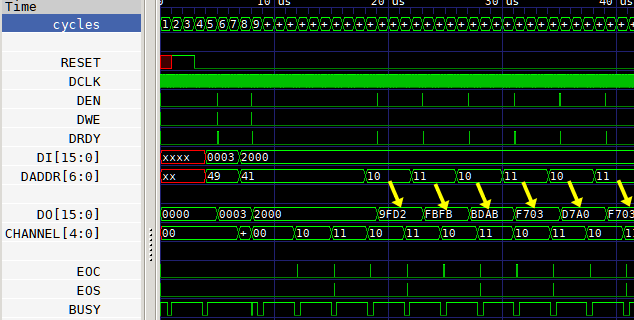

- RESETをトグルして、XADC内論理の初期化。当然RESET中に入力は確定させる。

- 観測対象チャンネルのCSR設定。

- 連続シーケンス(VAUXP[0][1]を交互にAD変換)のCSR設定後、AD変換が始まります。

- 最初の変換シーケンスが終わるまでデフォルトだと7[us]程度です。

- 後は1チャンネルに4[us]程度の時間で繰り返しCSRから値を読み出します。

Figure 2: 最初の変換シーケンスが終了するまで

Figure 3: AD変換値の繰り返し読み込み

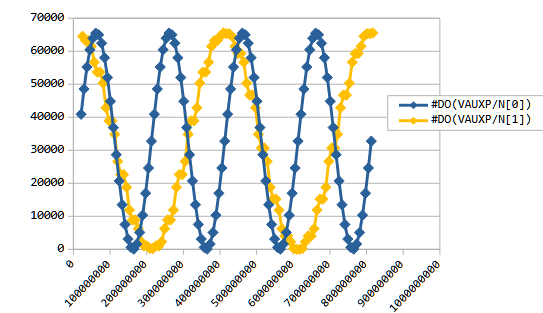

変換結果の取り込み

- テストベンチの $display で、読み出したチャンネル毎のAD変換値をログに落としています。Sim時間, チャンネル番号, DO出力10進変換値です。これが出力結果 run_xadc.log(zip) です。

VCD info: dumpfile wave.vcd opened for output. #TIME[ps] #DADDR[0] #DO[dec] 21000000 0 40914 25000000 1 64507 29000000 0 48555 33000000 1 63235 ...

|

Copyright(C) 2024 Altmo

本HPについて

本HPについて